# FPGA based Uniform Channelizer

### Implementation

By Fangzhou Wu

A thesis presented to the National University of Ireland in partial fulfilment of the requirements for the degree of **Master of Engineering Science**

> Department of Electronic Engineering National University of Ireland Maynooth March 2016

Research supervisors: Dr. Rudi Villing Head of department: Dr. Ronan Farrell

## Abstract

Channelizers are widely used in modern digital communication systems. Advanced uniform multirate channelization have been theoretically proved to be capable of reducing the computational load, with a better performance. Therefore, in this thesis, we implement these designs on a FPGA board for the sake of the comprehensive evaluation of resource usage, performance and frequency response.

The uniform filter-banks are one of the most essential unit in channelization. The Generalised Discrete Fourier Transform Modulated Filter Bank (GDFT-FB), as an important variant of basic a DFT-FB, has been implemented in FPGA and demonstrated with a better computational saving rather than traditional schemes. Moreover the oversampling version is demonstrated to have a better frequency response with an acceptable amount of extra resources. On the other hand, frequency response masking (FRM) techniques is able to reduce the number of coefficients. Therefore, the full FRM GDFT-FB and alternative narrowband FRM GDFT-FB are both implemented in FPGA platform, in order to achieve a better performance and hardware efficiency.

## **Declaration**

I hereby declare that this thesis is my own work and has not been submitted in any form for another award at any other university or institute of tertiary education. Information derived from the published or unpublished work of others has been acknowledged in the text and a list of references is given.

Signature

Date

## Acknowledgements

First of all, I'd like to thank my supervisor Dr. Rudi Villing. He has a strong sense of responsibility. Thank you for your supervision, kindness and patience. I am deeply grateful for all the help I received during the course.

And I am also very thankful to my parents for continuous support, love and understanding.

## **Table of contents**

| Abstract        | ii                               |

|-----------------|----------------------------------|

| Declaration     | iii                              |

| Acknowledger    | nentsiv                          |

| Table of conte  | ntsv                             |

| List of figures | ix                               |

| List of tables  | xiii                             |

| Chapter 1 Intro | oduction1                        |

| 1.1 Thesi       | is objective                     |

| 1.2 Thesi       | is contributions                 |

| 1.3 Thesi       | is outline                       |

| Chapter 2 Bac   | kground7                         |

| 2.1 Field       | Programmable Gate Array7         |

| 2.1.1 I         | ntroduction7                     |

| 2.1.1.1         | LUT9                             |

| 2.1.1.2         | Block RAM                        |

| 2.1.1.3         | DSP48s                           |

| 2.1.2           | Verilog HDL                      |

| 2.1.3           | Xilinx IP Cores                  |

| 2.1.4 H         | Fixed point DSP 12               |

| 2.2 Chan        | nelization technology            |

| 2.2.1 \$        | Single channel and multi-channel |

| 2.2.1.1         | Per-channel approach14           |

| 2.2.1.2         | Pipelined frequency transform15  |

| 2.2.1.3         | Polyphase filter-bank            |

| 2.2.2 H         | Hardware complexity comparison17 |

| 2.2.3 U         | Uniform Versus Non-uniform       |

| 2.3 Frequ       | ency Response Masking (FRM)      |

| 2.3.1 \$        | Subclass I filter                |

| 2.4 TETH        | RA standard                      |

| 2.5 Relat       | ed work                          |

| 2.6    | Concl     | usion                                               | 28 |

|--------|-----------|-----------------------------------------------------|----|

| Chapte | r 3 Criti | cally Sampled Uniform Wideband Channelization       | 30 |

| 3.1    | Introd    | uction                                              | 30 |

| 3.     | 1.1 D     | PFT-Filterbank (DFT-FB)                             | 30 |

| 3.     | 1.2 G     | eneralized DFT Filter-Bank (GDFT-FB)                | 32 |

| 3.2    | The F     | PGA implementation                                  | 35 |

| 3.2    | 2.1 B     | asic DFT-FB channelizer FPGA implementation         | 35 |

|        | 3.2.1.1   | Coefficients Mapping                                | 35 |

|        | 3.2.1.2   | Complex Signal Process in FPGA                      | 36 |

| 3.2    | 2.2 G     | DFT-FB Channelizer FPGA Implementation              | 39 |

|        | 3.2.2.1   | Complex modulation of prototype filter coefficients | 39 |

|        | 3.2.2.2   | Complex Filter Coefficients using the FIR Compiler  | 39 |

|        | 3.2.2.3   | Frequency Shift State Machine                       | 41 |

|        | 3.2.2.4   | Final Design                                        | 43 |

| 3.3    | FPGA      | Implementation Evaluation                           | 44 |

| 3.     | 3.1 Ir    | nplementation and test environment                  | 44 |

|        | 3.3.1.1   | Implementation specification                        | 44 |

|        | 3.3.1.2   | Xilinx Viretx-6 board overview                      | 46 |

|        | 3.3.1.3   | Implementation and test flow                        | 47 |

| 3.3    | 3.2 E     | valuation and Results                               | 48 |

|        | 3.3.2.1   | Frequency response                                  | 48 |

|        | 3.3.2.2   | EVM result                                          | 50 |

|        | 3.3.2.3   | Adjacent channel interference                       | 50 |

|        | 3.3.2.4   | Hardware usage                                      | 53 |

| 3.4    | Chapt     | er conclusion                                       | 53 |

| Chapte | r 4 Over  | sampled Uniform Wideband Channelization             | 55 |

| 4.1    | Introd    | uction                                              | 55 |

| 4.     | 1.1 A     | liasing problem and oversampling solution           | 55 |

| 4.     | 1.2 O     | versampled polyphase decomposition                  | 56 |

| 4.2    | Overs     | ampled DFT-FB (even stacked)                        | 57 |

| 4.2    | 2.1 H     | ligh level design                                   | 57 |

| 4.2    | 2.2 O     | versampled polyphase decimation FIR                 | 58 |

| 4.2    | 2.3 F     | IR block output samples rearrangement for the FFT   | 60 |

| 4.2    | 2.4 O     | versampled frequency shift state machine            | 62 |

| 4.2    | 2.5 F     | inal FPGA design                                    | 63 |

| 4.3    | Overs     | ampled GDFT-FB (odd-stacked)                        | 65 |

| 4.3.1          | Hig        | h level design                                               | 65  |

|----------------|------------|--------------------------------------------------------------|-----|

| 4.3.2          | Ove        | ersampled complex polyphase decimation FIR blocks            | 66  |

| 4.3.3          | Fina       | al FPGA design                                               | 66  |

| 4.4 F          | FPGA in    | nplementation evaluation                                     | 68  |

| 4.4.1          | Free       | quency response                                              | 68  |

| 4.4.2          | EV         | M result                                                     | 70  |

| 4.4.3          | Adj        | acent channel interference                                   | 70  |

| 4.4.4          | Har        | dware resource usage                                         | 71  |

| 4.5 0          | Chapter    | conclusion                                                   | 72  |

| Chapter 5      | FRM a      | nd the GDFT-FB                                               | 74  |

| 5.1 H          | Full FRI   | M applied to the GDFT-FB                                     | 74  |

| 5.1.1          | Intr       | oduction                                                     | 74  |

| 5.1.2          | The        | FPGA based full FRM DFT-FB (even stacked)                    | 76  |

| 5.1            | 1.2.1      | The high level FPGA design                                   | 76  |

| -              | 1.2.2      | The delay of second path design with an arbitrary fractional |     |

|                |            | der                                                          |     |

|                | 1.2.3      | Polyphase decomposed base filter                             |     |

|                | 1.2.4      | Phase shifting and addition state machine                    |     |

| 5.1.3          |            | FPGA based full FRM GDFT-FB (odd stacked)                    |     |

| -              | 1.3.1      | The high level FPGA design                                   |     |

| 5.2 N          |            | band FRM applied to the GDFT-FB                              |     |

| 5.2.1          | Intr       | oduction                                                     |     |

| 5.2            | 2.1.1      | Narrowband FRM                                               | 84  |

| 5.2<br>FE      | 2.1.2<br>3 | Alternative structure for oversampled narrowband FRM GDF 86  | FT- |

| 5.2.2<br>(ever |            | FPGA based alternative narrowband (oversampled) DFT-FB d)    | 87  |

|                | 2.2.1      | The overall design                                           |     |

|                | 2.2.2      | Efficient FIFO design of base FIR complier                   |     |

| 5.2.3          |            | FPGA based alternative narrowband (oversampled) GDFT-F       |     |

| (odd           |            | )                                                            |     |

| 5.2            | 2.3.1      | Theoretical structure                                        | 89  |

| 5.2            | 2.3.2      | FPGA design                                                  | 90  |

| 5.3 H          | Evaluati   | on and results                                               | 92  |

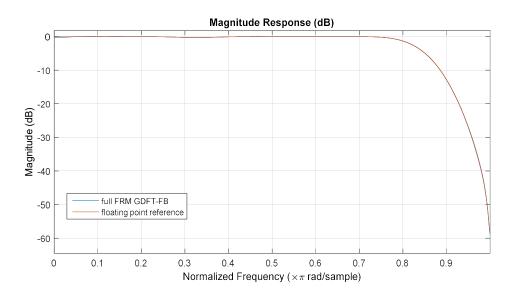

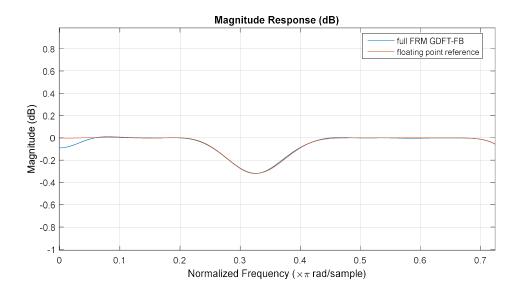

| 5.3.1          | Free       | quency response                                              | 93  |

| 5.3.2          | EVI        | M result                                                     | 96  |

| 5.3.3          | Adj        | acent channel interference                                   | 97  |

| 5.3.4 Hardware resource usage 100                                  |

|--------------------------------------------------------------------|

| 5.4 Chapter conclusion                                             |

| Chapter 6 Scaled up Evaluation 102                                 |

| 6.1 Scaling up of filter-banks 103                                 |

| 6.1.1 Scaling up critically sampled DFT-FB/GDFT-FB to 256 channels |

|                                                                    |

| 6.1.2 Scaling up alternative narrowband FRM DFT-FB/GDFT-FB to 256  |

| channels104                                                        |

| 6.2 Evaluation and Results                                         |

| 6.2.1 Frequency response                                           |

| 6.2.1.1 Critically sampled GDFT-FB104                              |

| 6.2.1.2 Alternative narrowband FRM GDFT-FB 106                     |

| 6.2.2 EVM and adjacent channel interference                        |

| 6.2.3 Hardware resource usage                                      |

| 6.3 Chapter conclusion                                             |

| Chapter 7 Conclusions and future work                              |

| 7.1 Summary 112                                                    |

| 7.2 Future work                                                    |

| 7.3 Conclusions                                                    |

| References                                                         |

## List of figures

| Figure 2.1 The typical internal architecture of FPGA                                                                                                        | . 8 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.2 FPGA Programmable Logic Block                                                                                                                    | 10  |

| Figure 2.3 Xilinx IP core GUI (Xilinx ISE 14.3)                                                                                                             | 12  |

| Figure 2.4 A 4 channels channelizer                                                                                                                         | 14  |

| Figure 2.5 Channelizer using per-channel approach to filter channels                                                                                        | 15  |

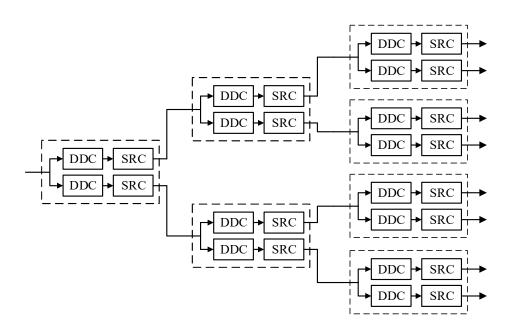

| Figure 2.6 Pipeline frequency transform structure of a binary tree with DDC followed by SRC.                                                                | 16  |

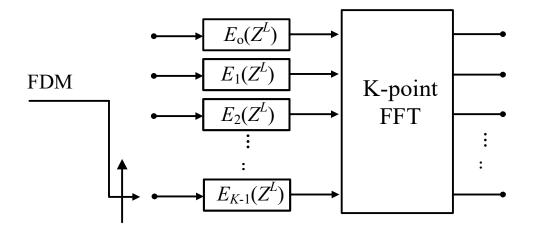

| Figure 2.7 The structure of the DFT-FB where <i>L</i> is the oversampling factor and $E_K(z^L)$ are the polyphase components of the prototype filter $H(z)$ | 17  |

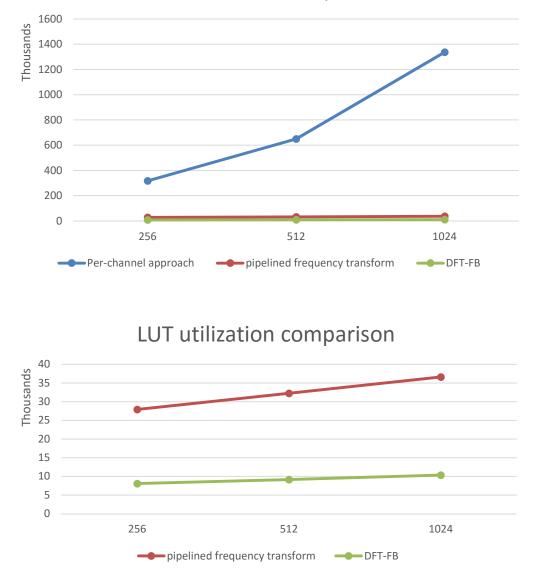

| Figure 2.8 The LUT utilization comparison                                                                                                                   | 18  |

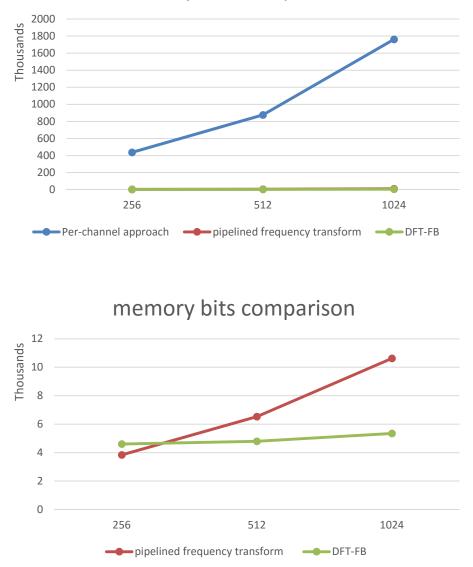

| Figure 2.9 the memory bit comparison                                                                                                                        | 19  |

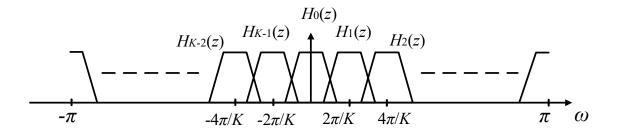

| Figure 2.10 The uniform filter-bank's frequency response                                                                                                    | 20  |

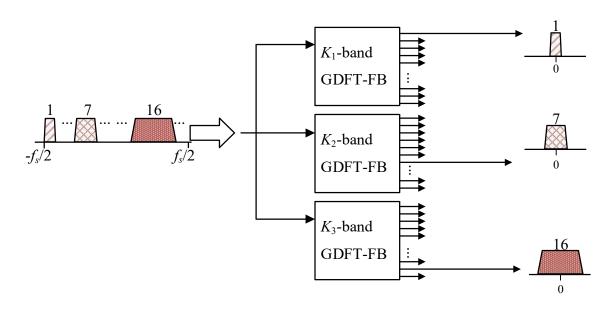

| Figure 2.11 P-GDFT non-uniform structure                                                                                                                    | 21  |

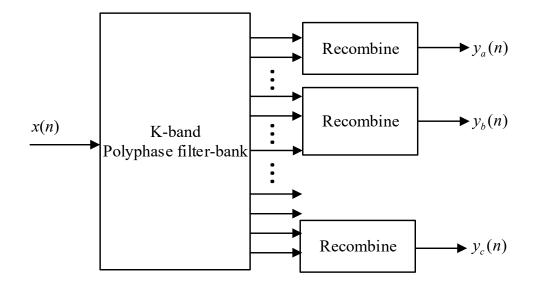

| Figure 2.12 Recombined GDFT-FB channelizer                                                                                                                  | 21  |

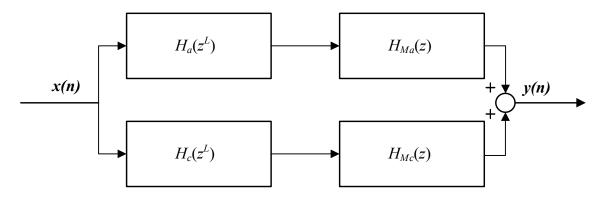

| Figure 2.13 Direct form of frequency response masking                                                                                                       | 22  |

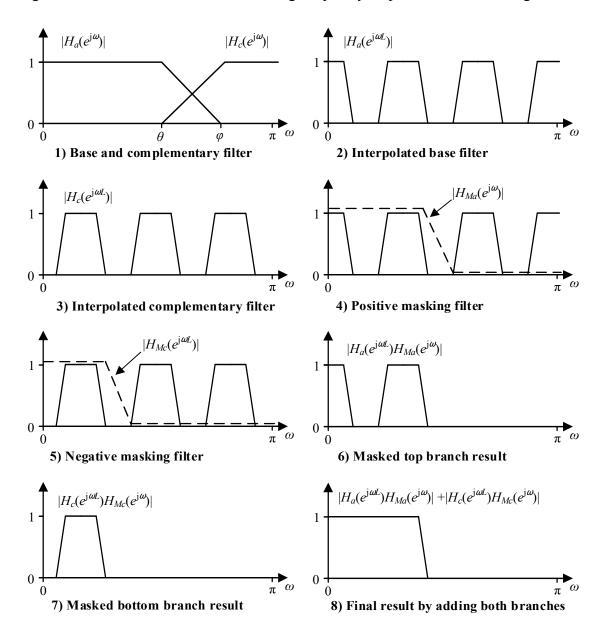

| Figure 2.14 The process of two branches filtering base on FRM                                                                                               | 23  |

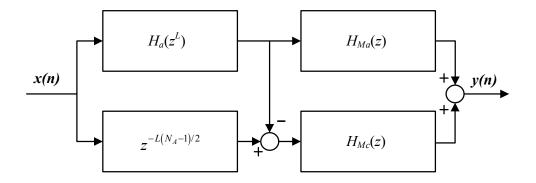

| Figure 2.15 Efficient implementation of FRM                                                                                                                 | 24  |

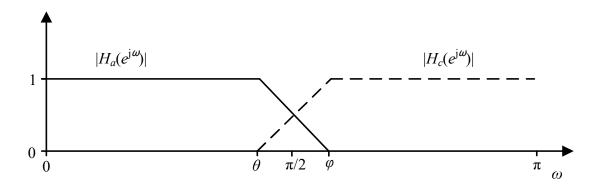

| Figure 2.16 Subclass I Filter frequency response                                                                                                            | 25  |

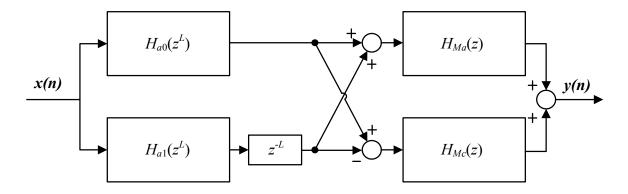

| Figure 2.17 The efficient FRM design with polyphase decomposition                                                                                           | 26  |

| Figure 3.1 The polyphase DFT modulated receiver                                                                                                             | 31  |

| Figure 3.2 DFT modulated filter-bank (DFT-FB)                                                                                                               | 32  |

| Figure 3.3 a) Even stacked channels, b) odd stacked channels                                                                                                | 33  |

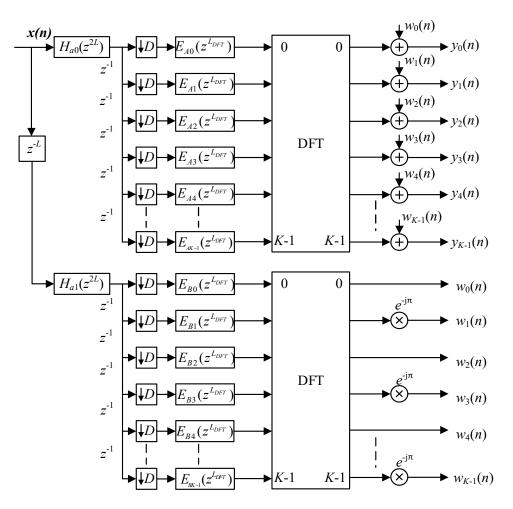

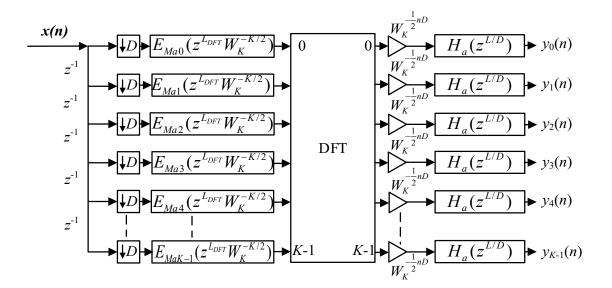

| Figure 3.4. GDFT modulated filter bank (GDFT-FB)                                                                                                            | 34  |

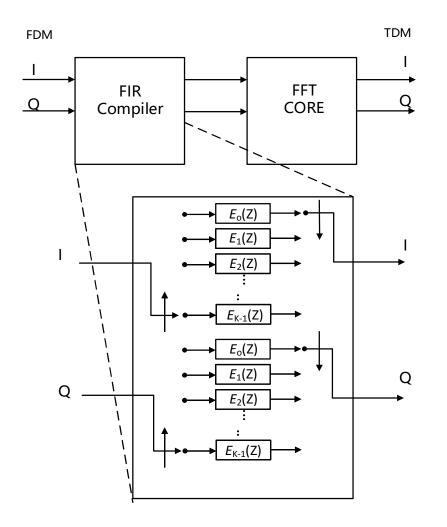

| Figure 3.5 The DFT-FB FPGA design for the complex input                                                                                                     | 36  |

| Figure 3.6 The FPGA implementation of DFT-FB                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

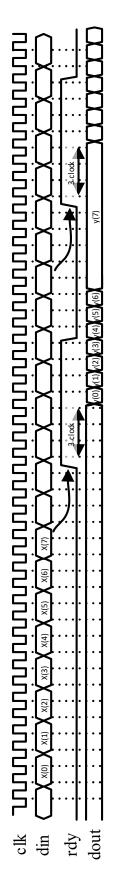

| Figure 3.7 The waveform shows that the output of FIR complier has a 3 clock delay from rdy signal                                                                                                                                          |

| Figure 3.8 cross coupling of complex signal filtering                                                                                                                                                                                      |

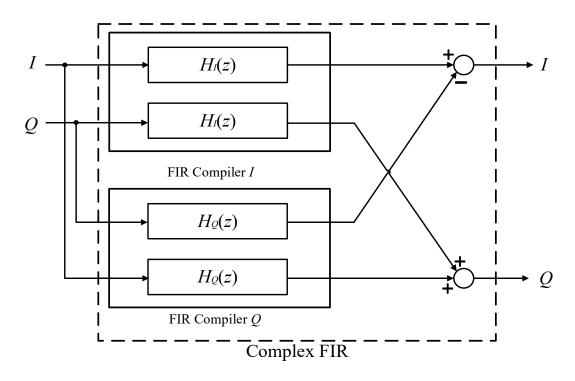

| Figure 3.9 Complex FIR implemented using cross-coupled FIR compiler IP core                                                                                                                                                                |

| Figure 3.10 Frequency shifting state machine work flow                                                                                                                                                                                     |

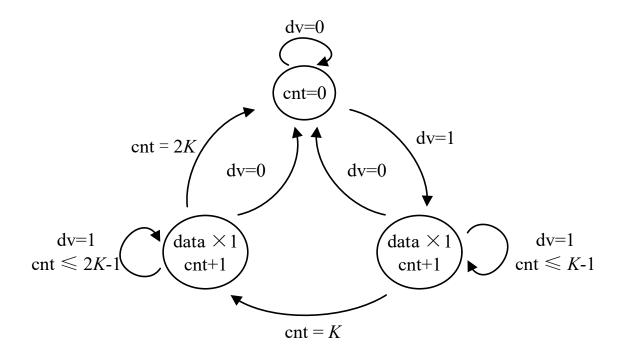

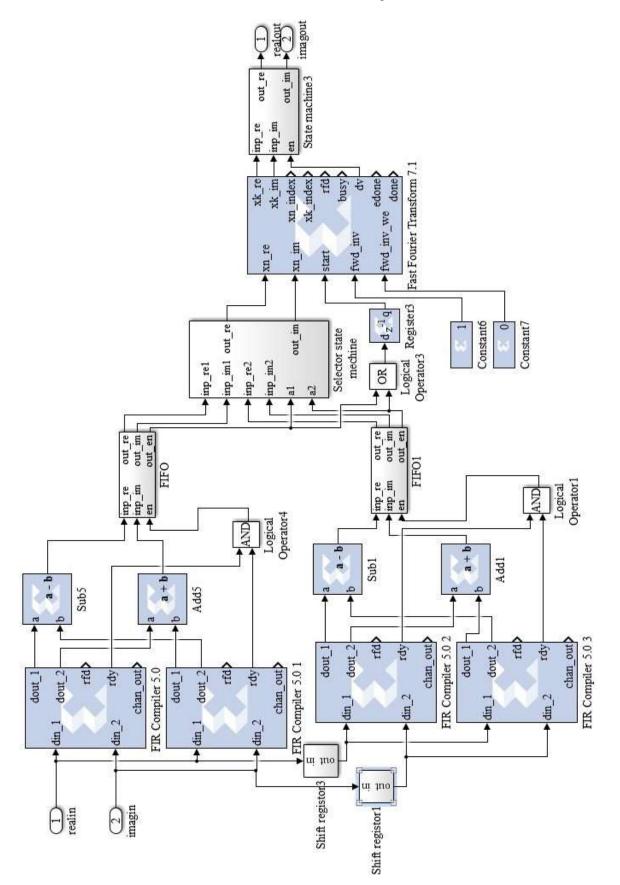

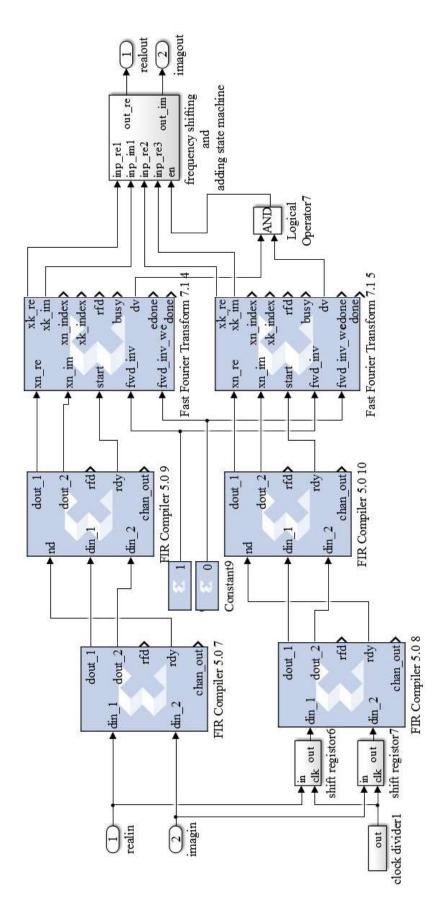

| Figure 3.11 FPGA implementation of the GDFT-FB 44                                                                                                                                                                                          |

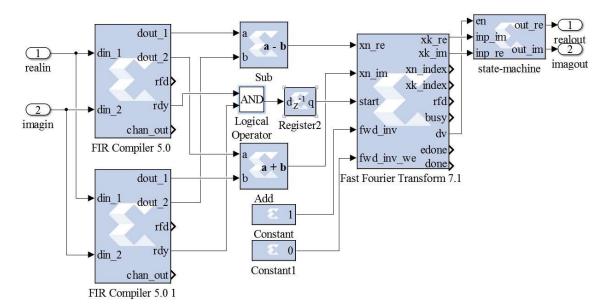

| Figure 3.12 The Filter-bank development and testing flow                                                                                                                                                                                   |

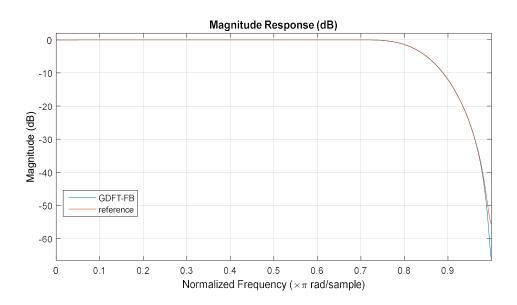

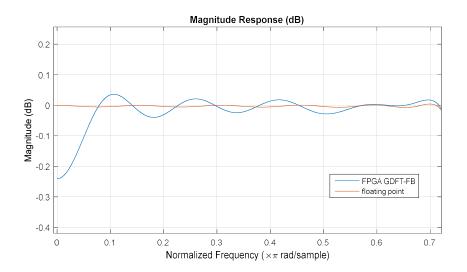

| Figure 3.13 Sub-band frequency response of the FPGA Fixed Point GDFT-FB (blue line) compared to a floating point GDFT-FB reference (red line)                                                                                              |

| Figure 3.14 Passband comparison between FPGA based GDFT-FB and its floating point reference                                                                                                                                                |

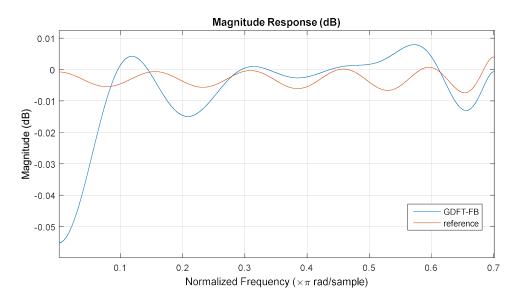

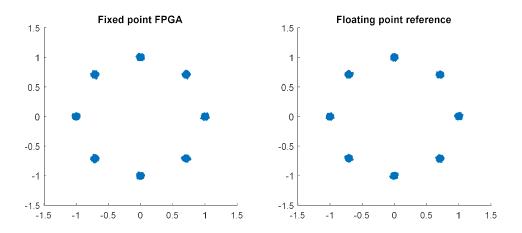

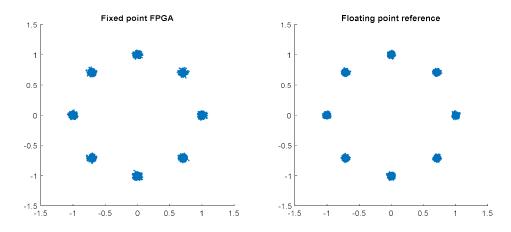

| Figure 3.15 The QPSK modulation constellation after the FPGA based GDFT-FB (left), and the QPSK modulation constellation after a floating point GDFT-FB 50                                                                                 |

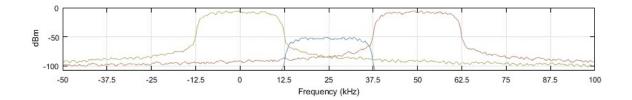

| Figure 3.16 The even stacked testing wideband signal of adjacent channel interference when $C/I_a = -45$ dB                                                                                                                                |

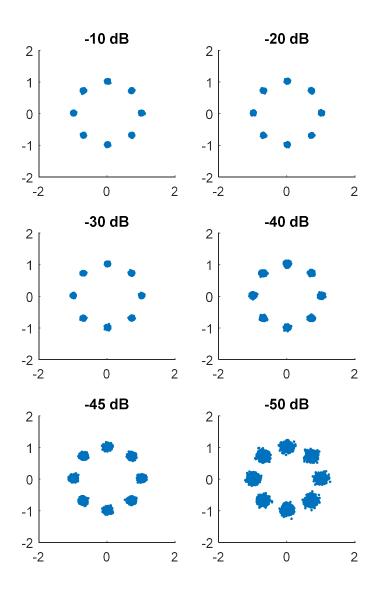

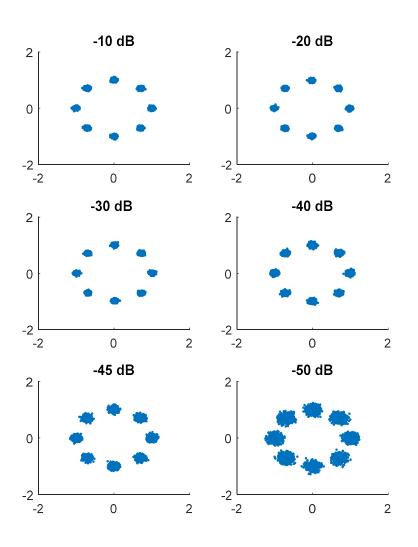

| Figure 3.17 Modulation constellation of a channel of interest subjected to different levels of adjacent channel interference after extraction by the FPGA GDFT-FB 52                                                                       |

| Figure 4.1The interaction of a filter with its images in the decimated sub-band output a) exhibits aliasing when critically sampled due to overlapping images whereas b) oversampling separates the images and greatly reduces aliasing 56 |

| Figure 4.2 Commutator with interpolator in oversampled design 57                                                                                                                                                                           |

| Figure 4.3 Converting 2x oversampled 4 channels GDFT-FB input distribution to A) a functionally equivalent version based on (4.4) and B) an equivalent version using commutators                                                           |

| Figure 4.4 FIR selector state machine mapping the output of two FIR blocks to a single TDM output suitable for input to the FFT IP core                                                                                                    |

| Figure 4.5. Oversampled polyphase decimation FIR implemented using real or complex critically sampled polyphase decimation FIR blocks (based on the FIR compiler IP core)                                                                  |

| Figure 4.6 Frequency shifting state machine work flow                                                                                                                                                                                      |

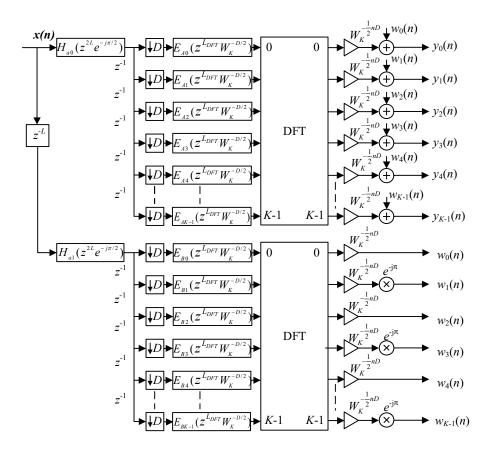

| Figure 4.7 the FPGA architecture diagram of 2x oversampled DFT-FB (even stacked)                                                                                                                                                           |

| Figure 4.8 the FPGA architecture diagram of 2x oversampled GDFT-FB (even stacked)                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

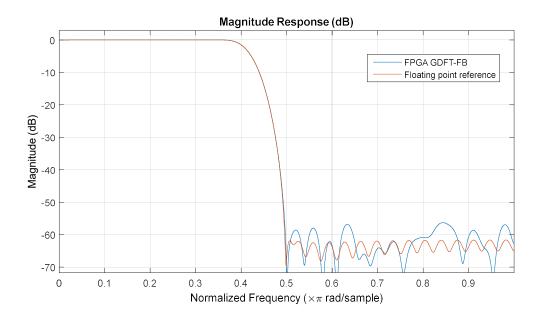

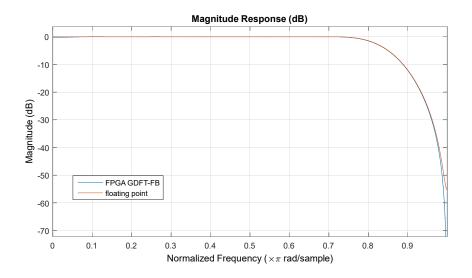

| Figure 4.9 Frequency response of one sub-band of the FPGA-based 16-bit 16-<br>channel 2x oversampled GDFT-FB. The FPGA based (fixed point) response<br>(blue) and floating point GDFT-FB reference implementation (red) are both<br>shown |

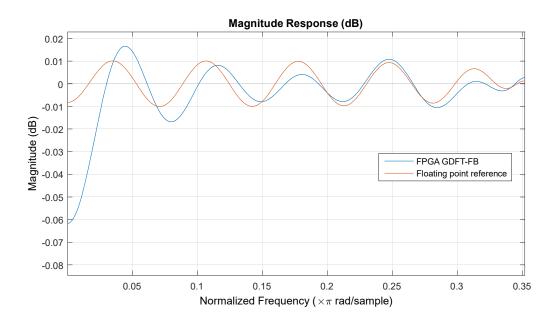

| Figure 4.10 Passband comparison between 16-bit FPGA GDFT-FB (blue line) and its floating point reference (red line)                                                                                                                       |

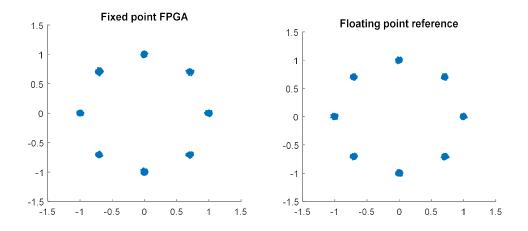

| Figure 4.11 The pi/4 DQPSK modulation constellation of the FPGA based 2x oversampled GDFT-FB output (left), and the equivalent constellation of the floating point GDFT-FB reference output (right)                                       |

| Figure 5.1 Full FRM DFT-FB                                                                                                                                                                                                                |

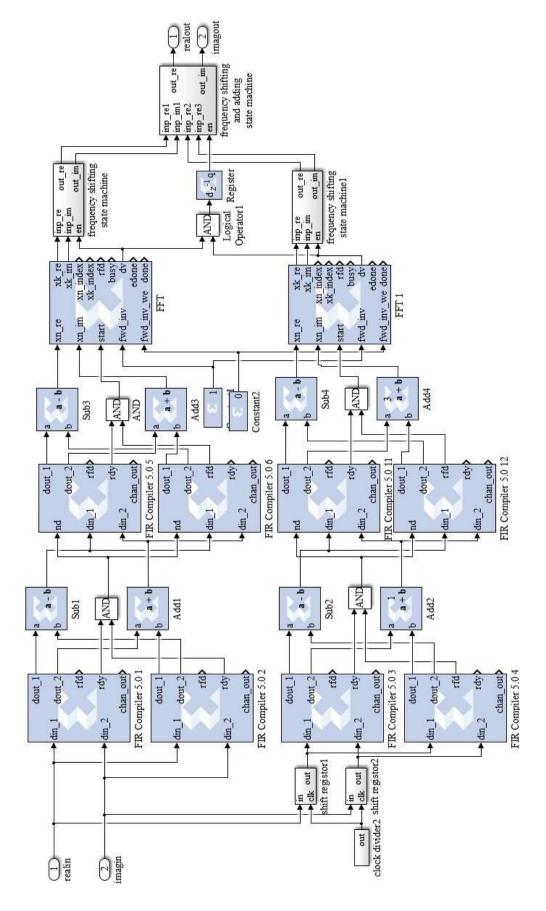

| Figure 5.2 The FPGA based even stacked full FRM DFT-FB 77                                                                                                                                                                                 |

| Figure 5.3 Full FRM GDFT-FB (odd stacked, with $k_0=1/2$ and $n_0=0$ )                                                                                                                                                                    |

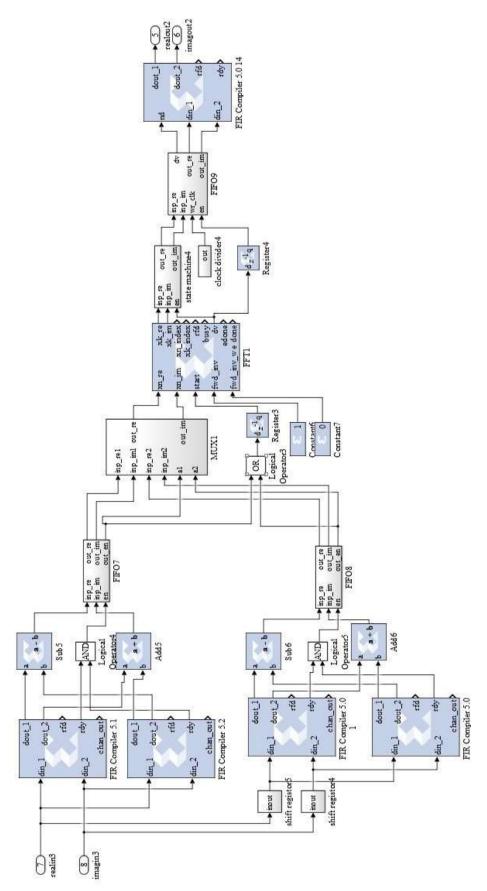

| Figure 5.4 The odd stacked full FRM GDFT-FB                                                                                                                                                                                               |

| Figure 5.5 The process of narrow-band FRM filter                                                                                                                                                                                          |

| Figure 5.6 Efficient oversample GDFT-FB with narrowband FRM                                                                                                                                                                               |

| Figure 5.7 2x oversampled alternative narrowband FRM GDFT-FB 88                                                                                                                                                                           |

| Figure 5.8 The FIFO used to slow the FFT output for output sub-band FIR compiler IP cores                                                                                                                                                 |

| Figure 5.9 Odd stacked GDFT-FB with narrowband FRM technology                                                                                                                                                                             |

| Figure 5.10 FPGA implementation of odd stacked narrowband GDFT-FB 91                                                                                                                                                                      |

| Figure 5.11 Frequency response of the FPGA based full FRM GDFT-FB sub-band (blue) compared to the equivalent floating point reference implementation (red) 93                                                                             |

| Figure 5.12 Passband comparison between the FPGA based full FRM GDFT-FB (blue) and its equivalent floating point reference implementation (red)                                                                                           |

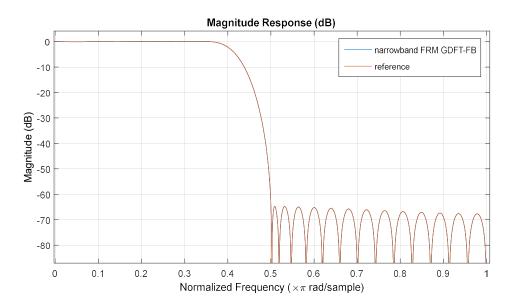

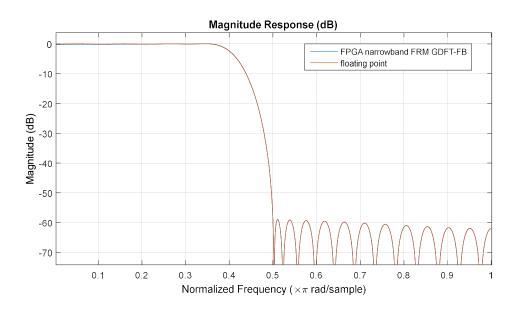

| Figure 5.13 Frequency response of the FPGA based 16-channel alternative narrowband FRM GDFT-FB (blue) compared to its floating point reference implementation (red)                                                                       |

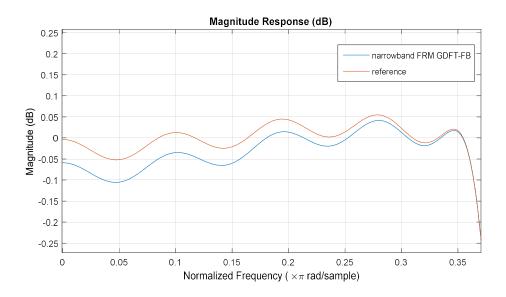

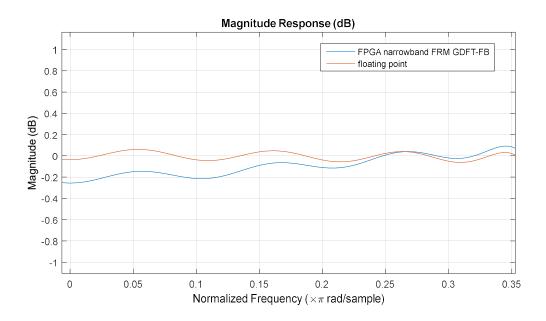

| Figure 5.14 Passband comparison between the FPGA based alternative narrowband FRM GDFT-FB (blue) and its floating point reference implementation (red)                                                                                    |

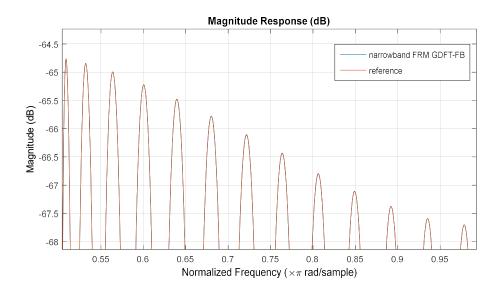

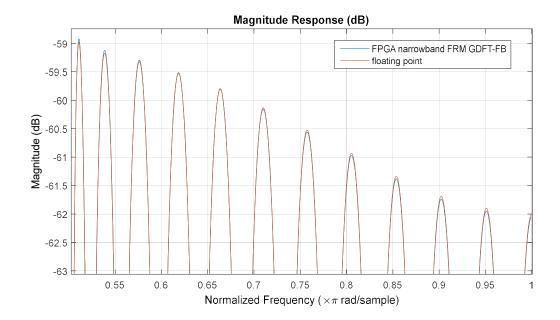

| Figure 5.15 stop band comparison between the FPGA based alternative narrowband FRM GDFT-FB (blue) and the equivalent floating point reference implementation (red)                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

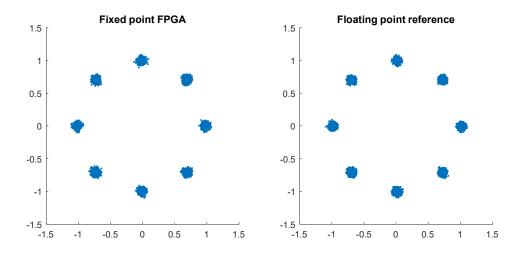

| Figure 5.16 The QPSK modulation constellation of the FPGA based full FRM GDFT-FB output (left), and the QPSK modulation constellation of a reference floating point full FRM GDFT-FB output (right)     |

| Figure 5.17 The QPSK modulation constellation of the FPGA based narrowband GDFT-FB output (left), and the QPSK modulation constellation of a reference floating point narrowband GDFT-FB output (right) |

| Figure 5.18 Modulation constellation of the FPGA based full FRM GDFT-FB at different adjacent channel interference levels                                                                               |

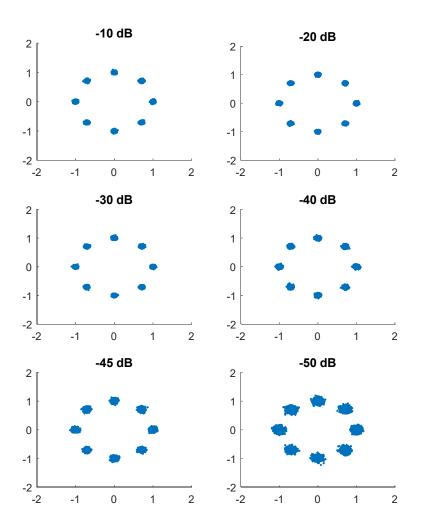

| Figure 5.19 Modulation constellation of the FPGA based alternative narrowband GDFT-FB at different adjacent channel interference levels                                                                 |

| Figure 6.1 Frequency response of critically sampled GDFT-FB comparing the fixed point FPGA implementation (blue) to the floating point reference implementation (red)                                   |

| Figure 6.2 Passband comparison between the FPGA based GDFT-FB (blue line) and floating point reference implementation (red line) 105                                                                    |

| Figure 6.3 Frequency response of the FPGA based alternative narrowband FRM GDFT-FB (blue) and floating point reference implementation (red) 106                                                         |

| Figure 6.4 Passband comparison between FPGA based alternative narrowband FRM GDFT-FB (blue) and the floating point reference implementation (red line)                                                  |

| Figure 6.5 Stop band comparison between the FPGA based alternative narrowband FRM GDFT-FB (blue) and the floating point reference implementation (red)                                                  |

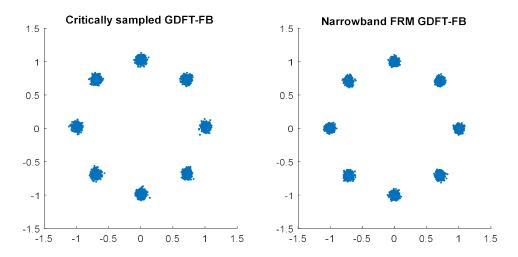

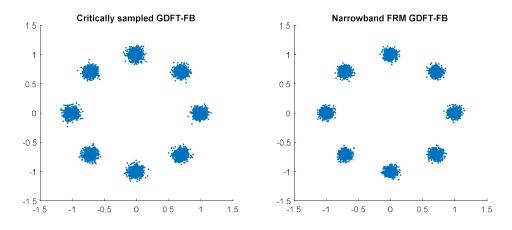

| Figure 6.6 The EVM constellation of critically sampled GDFT-FB and alternative narrowband FRM GDFT-FB                                                                                                   |

| Figure 6.7 The EVM constellation of the FPGA based critically sampled GDFT-<br>FB and alternative narrowband FRM GDFT-FB with $C/I_a$ = -45 dB 109                                                      |

## List of tables

| Table 2.1 The hardware comparison of per-channel approach, pipeline frequencytransform DFT-FB17                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1 Test filter-banks' specifications                                                                                                                |

| Table 3.2 Virtex-6 XC6VLX240T-1FFG1156 FPGA board resources summary 47                                                                                     |

| Table 3.3 The EVM performance of a 16 channel GDFT-FB based on FPGA 50                                                                                     |

| Table 3.4 RMS and Peak EVM for a channel of interest subjected to different adjacent channel interference level extracted using the FPGA based GDFT-FB. 53 |

| Table 3.5 Resource usage for the (even stacked) DFT-FB and (odd stacked)GDFT-FB channelizers53                                                             |

| Table 4.1 The EVM performance of an FPGA-based 16-channel 2x oversampledGDFT-FB70                                                                          |

| Table 4.2 EVM result of FPGA 2x oversample GDFT-FB under different adjacent channel interference level       71                                            |

| Table 4.3 Even and odd stacked 2x oversampled GDFT-FB FPGA resourcesusage                                                                                  |

| Table 5.1 The EVM performance of both FPGA based designs: the 16-channelfull FRM GDFT-FB and the alternative narrowband GDFT-FB                            |

| Table 5.2 EVM results of the FPGA based full FRM GDFT-FB and alternative narrowband FRM GDFT-FB at different adjacent channel interference levels 99       |

| Table 5.3 Hardware usage of full FRM GDFT-FB and alternative narrowbandFRM GDFT-FB.100                                                                     |

| Table 6.1 Hardware usage of all FPGA based 16-channel filter banks         implemented to date         102                                                 |

| Table 6.2 the EVM result of critically sampled GDFT-FB and alternativenarrowband FRM GDFT-FB108                                                            |

| Table 6.3 the EVM result of critically sampled GDFT-FB and alternative narrowband FRM GDFT-FB under -45 dB adjacent channel interference 109               |

| Table 6.4 Resource usage comparison of critically sampled GDFT-FB and alternative narrowband FRM GDFT-FB when configured for 256 channels 110              |

## **Chapter 1**

## Introduction

DSP (Digital Signal Processing) has been a rapidly developing aspect of modern technology and has become an indispensable part of many products that we use in our modern lives [1]. Multirate signal processing is one of the major branches of DSP. It is a technology that finds use in signal processing systems where various sub-systems with differing sample or clock rates need to be interfaced together. At other times multi-rate processing is used to reduce the computational overhead of a system. It thus confers advantages of: (1) greatly reducing the cost of hardware; (2) providing an improved implementation performance [2]. Multirate digital filters and filter-banks are two widely used applications in multirate signal processing. They are mostly used in the field of speech processing, image processing and communications [3, 4].

Polyphase filters and filter-banks are one of the outstanding channelization examples to represent multirate digital filters [5]. They offer a significant reduction in processing complexity by way of separating the input signals into several channels. Polyphase filter-bank are widely used in industry, such as in the MP3 audio format [6] and in the digital receiver analysers that are discussed in this thesis.

The theory of polyphase filter banks was formed in the 80s and has been further developed since then [7-10], to have more configurations that can be adapted to more complicated tasks [11]. However, only a few of the further developments have been realized on hardware platforms, such as on a field-programmable gate arrays (FPGA) and DSP processors.

The reason of implementing the theoretic polyphase filter-bank on an FPGA is that an FPGA has sufficient resources and a high performance that can allow the implementation of a large number of DSP algorithms very efficiently compared to a single chip processor [12]. In data flow applications, no instructions need to be fetched from memory, and not many read/write operation from memory are required since most of the data has directly

been inserted into the register, because the FPGA input samples are flowing through the programmed logic cells. In addition, FPGA architectures allow developers to exchange resources for speed by configuring more logic resources to perform parallel processing [13].

Several polyphase DFT-FB (Discrete Fourier Transform-FilterBank) FPGA implementations have already been realized [14-17]. However these FPGA DFT-FBs design the architectures from a very basic level. The designs may lack flexibility due to limited number of channels and the amount of resources that can be exchanged for speed in different computational complexity scenarios. In the case of a change in the design requirements, considerable more work could be needed to adjust the design. This could potentially hinder further complicated development based on the implementation of a DFT-FB FPGA architecture. Thus some of the complex and resource demanding algorithm components are replaced by IP cores among the designs in this thesis.

Most of the FPGA implementations are focused on the basic Discrete Fourier Transform-FilterBank (DFT-FB). There are also some further developments based on DFT-FB, which are proved to have a better DSP performance or a better hardware efficiency. However they haven't been implemented on the FPGA platform in literature. Therefore in this thesis, these DFT-FB based designs are going to be built on FPGA, then a thorough evaluation will be evaluated to see if they are practical in terms of being useful for industry applications.

### **1.1** Thesis objective

The objective in this thesis is to design and implement a new set of polyphase filter-bankbased uniform channelizers on an FPGA platform. The designs will cover critically sampled GDFT-FBs (Generalized DFT modulated Filter Bank), oversampled GDFT-FBs, GDFT-FBs with full FRM technology and GDFT-FBs with narrow-band GDFT-FBs. Every type of filter contains both odd and even stacked channel allocation configurations. Most of the new designs in this thesis take advantage of Xilinx IP cores to simplify and boost the development, and ensure that other larger DSP FPGA designs based on these uniform channelizers are more convenient. We will also discuss the implementation of the theory that has been proposed already, along with the problems that developers face when realizing the FPGA channelizers and possible solutions to these. Later sections in this thesis will cover the possibility for optimizations in the architecture for better efficiency, along with a performance and results' analysis, an assessment of the hardware resource usage, and an evaluation of whether the design is or is not feasible with current communication standards.

### **1.2** Thesis contributions

In this thesis, several kinds of polyphase filters and new filter-bank designs based on the polyphase filter-bank will be implemented on an FPGA to evaluate their performance, system complexity, resource usage and their feasibility for industrial scenarios.

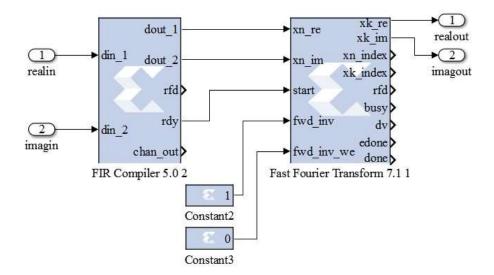

Developers are now willing to take advantage of pre-built blocks e.g. IP cores, as the complexity of modern digital systems increases at a remarkable speed that is driven nowadays by the challenging pressures of time-to-market. This is one of the design reuse methodologies [18]. These IP cores give a great convenience when designing or tuning a new FPGA architecture. Complicated processing elements can be designed to either process samples in parallel in order to have an improved processing speed, or process then serially for an efficient resource usage. The works presented in this thesis replace the FIR filters and FFT elements with IP cores of a basic DFT-FB, and introduce further developed polyphase filter-banks (GDFT-FB, oversampled GDFT-FB, full FRM GDFT-FB and alternative narrowband FRM GDFT-FB) implementation by using IP cores, in order to have a significant reduction in the cost of design.

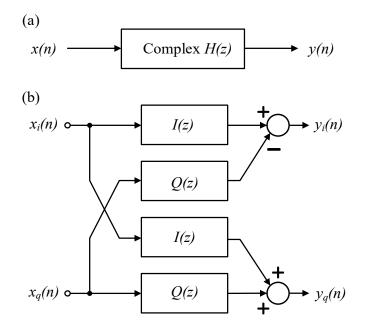

GDFT-FB is a generalized version of DFT-FB, it allows the polyphase filter-bank to have more configurations such as facilitating phase shifting and adjustable centre frequency. This design flexibility leads to an odd-stacked channel allocation filter-bank that has a better spectrum usage. Therefore, the FPGA implementation of GDFT-FB is presented in this thesis. A new designed complex FIR block which can filter samples with complex coefficients is also introduced and explained in detail, which is the essential part of a GDFT-FB. GDFT-FB also provides the option to design the polyphase filter-bank in an oversampled configuration. This allows a better reconstruction of signals by reducing the aliasing problem between adjacent channels. Therefore the oversampled GDFT-FB FPGA implementation is presented in this work. A mathematical equivalent of a sample distribution model as a theoretical expression and diagram are developed for the FPGA architecture in order to fit IP cores in an oversampled configuration. Furthermore, an oversampled odd-stacked channel allocation GDFT-FB design is also implemented on the FPGA to have a better spectrum usage.

Apart from the polyphase filter-bank, FRM (Frequency Response Masking) filter technology also provides a significant computational reduction to produce an equivalent set of filtering results. The goal of combining into an FPGA design the FRM with the polyphase filter-bank will further reduce the number of coefficients required, and so the even and odd stacked channel allocations can be easily achieved. Thus, eventually a very efficient oversampled GDFT-FB with narrow-band FRM technology design in FPGA (both even and odd stacked) has been realized in this work.

Besides the high level FPGA implementation, some of adjustments and tweaks to fit IP cores to the new development of filter-banks, and hardware optimization to some of the models is also introduced in each design according to the type of the filter-bank.

Then, evaluations are performed of all the new developed filter banks, in a small scale of 16 channels. Evaluation includes frequency response, EVM (Error Vector Measurement), adjacent channel interference and hardware resources, in order to test their accuracy, performance and hardware efficiency.

Lastly, another similar evaluation of 256-channel configuration are performed to critically sampled DFT-FB/GDFT-FB and alternative narrowband FRM DFT-FB/GDFT-FB, in order to find which filter-bank technology is the most feasible and capable regard to industry scenario, because they have fairly good performance and yet with efficient hardware usage.

The summary of contributions of this thesis is as following:

- Replacing FIR filters and FFT elements with pre-built IP cores in the basic DFT-FB design, and introduce further developments of GDFT-FB, oversampled GDFT-FB, full FRM GDFT-FB and alternative narrowband FRM GDFT-FB implementations by using IP cores, in order to have a significant reduction in the cost of design.

- Introducing the FPGA design of generalized version of DFT-FB, i.e. GDFT-FB, which leads a better spectrum usage with the odd-stacked channel allocation.

- New designed oversampled GDFT-FB (in both even and odd stacked channel allocation) has also been designed in FPGA, in order to have a better signal reconstruction by reducing the aliasing between adjacent channels.

- Introducing the FPGA designs of two polyphase filter-banks design combined with FRM filter technology -- Full FRM GDFT-FB and narrow-band FRM GDFT-FB, to have a further efficiency in terms of hardware usage.

- The evaluation with 16-channel configuration are performed of all the new designed filter banks in order to test their accuracy, performance and hardware efficiency. Then the evaluation with 156 configuration are performed to critically sampled DFT-FB/GDFT-FB and narrowband FRM DFT-FB/GDFT-FB, in order to find the most feasible and capable filter-bank technology regard to industry scenario.

### **1.3** Thesis outline

The rest of the chapters are organized as follows:

Chapter 2 introduces the literature on which the work of this thesis is based. Moreover, an overview of FPGA architecture is presented, along with some material that may be needed to support the discussion of work in this thesis. Furthermore, the concept of polyphase filters is presented, as this is the base of the new design of GDFT-FB, oversampled GDFT-FB, and GDFT-FB applied with FRM.

Chapter 3 mainly presents the implementation of odd-stacked GDFT-FB that was developed from DFT-FB. Moreover, a new method is introduced to deal with the complex coefficients in FPGA design, as the coefficient has been complex modulated. Furthermore, some tweaks and an additional design which helps in adapting the FPGA design to fit the odd-stack configuration and complex operations are presented as well. Finally, there is test of the accuracy of the GDFT-FB design and its hardware usage, through a simulation test on a 16-channel FPGA architecture.

Chapter 4 applies the oversampled design to the polyphase filter-banks in order to have a better recovery of the input signal. The oversampled filter-bank FPGA realization depends on a parallel FIR Filter design. The oversampled configuration has been applied to the odd-stack GDFT-FB as well, which brings further design complexity. The performance and hardware usage is also tested on a FPGA simulation with a 16 channel configuration.

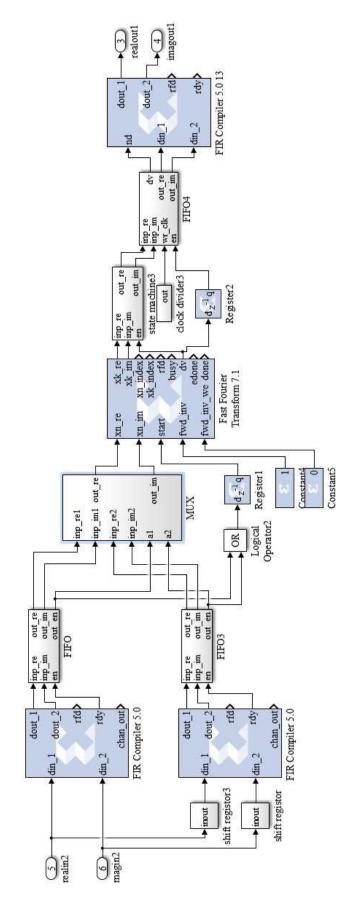

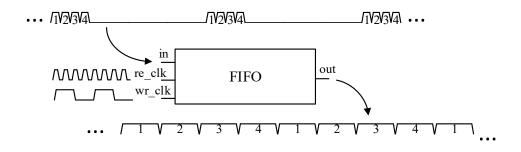

Chapter 5 introduces a computational saving FRM (Frequency Response Masking) technology and a combinational design with a polyphase filter-bank has been implemented on an FPGA. The FRM's two path structure leads to two GDFT-FB filter-banks in the system. The specially designed FIFO can handle the sample rate change due to the 2 stage structure of FRM. Additionally, the complex design allows the FPGA architecture to cope with odd-stack channel allocation. Finally, a very efficient oversampled alternative narrowband FRM GDFT-FB is introduced and developed on the FPGA. The FPGA simulation test is carried out again with both of the new designs that include the FRM for a configuration of 16 channels.

Chapter 6 shows the evaluation and comparison of the new filter-banks designs for a large number of channels. The resource usage, frequency response, EVM (Error Vector Measurement) and adjacent channel interference are the key specifications for analysis. Additionally, this chapter shows the advantages, drawbacks and practicality of these designs.

Chapter 7 gives the summary of the thesis, and point out several future works that can be developed based on the work presented. Finally, the conclusions of the work is presented.

## **Chapter 2**

## Background

### 2.1 Field Programmable Gate Array

#### 2.1.1 Introduction

Field Programmable Gate Array (FPGA) technology continues to advance rapidly since its invention by Xilinx in 1984. The worldwide market of FPGA is anticipated to be 9.8 billion dollars by 2020 [19]. Today FPGAs have become so popular, that in many areas they have replaced custom ASICs (Application Specific Integrated Circuits) and processors in the field of signal processing.

From the most basic point of view, FPGAs are reprogrammable silicon chips. It is an alternative physical architecture to implement digital logic in systems. By using prebuilt logic blocks, the prefabricated silicon chips can be programmed electrically to implement any custom digital hardware functionality by the developer or user. The design is developed in software on a computer, and then compiled to a configuration file that contains the connections of how the components are wired together. In addition, FPGAs can be reconfigured multiple times. The FPGAs are usually programmed and configured using HDL (Hardware Description Languages), such as Verilog and VHDL, like that used for ASICs.

FPGAs not only provide a lot of flexibility to the digital system design, but also give high speed and increased reliability. Unlike processors, FPGAs have a purely parallel processing architecture, which can provide increased speed. Moreover, adding more functions may not affect the speed of the system [20]. Thus FPGA is preferred in a variety applications that are computing intensive - like audio processing, medical electronics and digital signal processing [21-26]. The basic FPGA architecture consists of three important

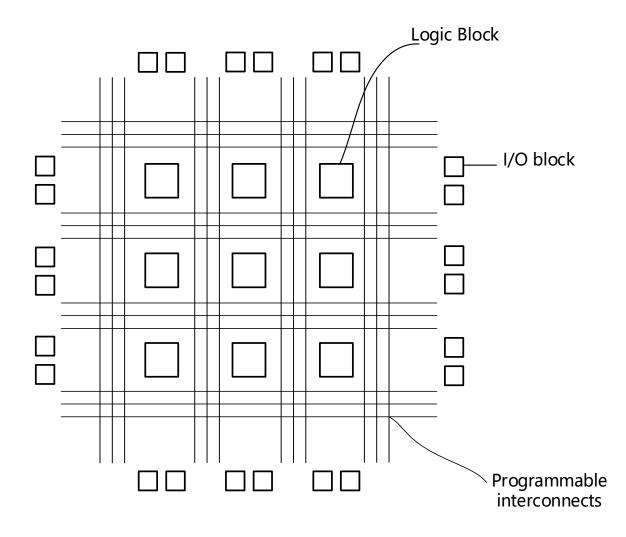

components: programmable logic block, programmable interconnection and I/O blocks [27]. Figure 2.1 illustrates a typical architecture of a FPGA.

Figure 2.1 The typical internal architecture of FPGA

#### • Programmable logic block

The programmable logic blocks are aimed to provide the basic functions and storages recourses to the digital system. The FPGA logic blocks are normally based on the combination of transistor pairs called *slices*, which contain basic logic gates like AND or XOR, multiplexers, look-up tables (LUTs) and wide-fanin AND-OR structure. Some modern FPGAs contain a more complex mixture of different of logics which can be used to do certain functions, like multipliers or multiplexers.

#### • Programmable interconnection

The purpose of the programmable interconnection of a FPGA is to make connections among the logic blocks and I/O blocks to match the user defined in the design. It uses various lengths of wire segments to interconnect through electrically programmable switches. Wire segments may consist of multiplexers, pass transistors and tri-state buffers to form the desired connections.

#### • I/O blocks

The components of FPGAs, such as logic blocks, require to have interaction with external components off the FPGA chip through the interface called I/O blocks. The I/O blocks are located around the boundary of the FPGA architecture. They play important roles, and occupy about 40% of the FPGA area. Normally they consist of an input buffer and an output buffer with three states, controlled by pull-up and pull-down resistors.

In recent years, further development has been carried out using the commercial FPGA architecture. Block RAMs, DSP48s, multipliers and other special function blocks are embedded into the FPGA chips for some high frequency or multiplications needed scenarios, such as high speed digital signal processing.

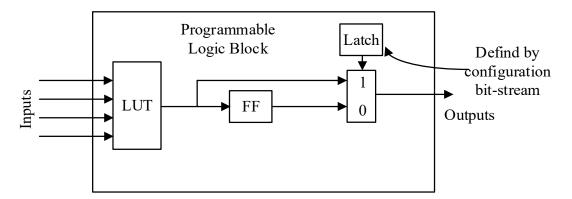

#### 2.1.1.1 LUT

Much of the logic in programmable logic block is built up with Look Up Tables (LUTs) by using a small amount of Random Access Memory (RAM). A LUT is basically a table that can determine the output from any given set of inputs. It works just as a truth table in terms of combinational logic. The truth table is a pre-defined output list for any input combinations. Thus no matter how complicated the combinational logics in a FPGA design are, LUTs can implement them with a small amount of resources. Figure 2.2 illustrates an architecture of a 4-input LUT in a programmable logic block.

Background

Figure 2.2 FPGA Programmable Logic Block

#### 2.1.1.2 Block RAM

A block RAM is a dedicated two port memory containing Kbs of RAM and can't be used to implement digital logics. It is the RAM embedded throughout the FPGA for data storage. Xilinx FPGA consists of 2 columns of block RAM. Dual-port allows separate reading and writing. It can also be configured to divide the memory into different width sizes: 1x36Kb or 2x18Kb. Block RAM is excellent for First-In/First-Out (FIFO) implementation. Larger memory blocks can be obtained by cascading multiple block RAMs. The maximum word-length data path a block RAM can handle is 18 bits.

#### 2.1.1.3 DSP48s

Modern FPGA architectures have been further developed to increase the speed of multiplication, addition and other operations highly needed for DSP [28]. The Xilinx Virtex-6 family FPGA board has been brought out along with slice embedded in it. The basic structure and procedure of this piece of slice is called Multiply Accumulate (MAC) function, and it is widely used to implement DSP processing in hardware. For example, the DSP48s slice includes adder, subtractors, accumulator and coefficient register, which provide high power efficiency and high performance. Each DSP48s slice is equivalent to more than 500 programmable logic blocks, only consumes about 1/10<sup>th</sup> of the power of the equivalent logic hardware design, and runs up to 600 MHz. In addition, the new added pre-adder in Virtex-6 board can be very useful in symmetric FIR filtering and other particular operations [29].

Background

#### 2.1.2 Verilog HDL

Verilog is one of the two most widely used HDLs (Hardware Description Language) used by integrated designers all over the world. The other is called VHDL.

HDL allows developers simulate their FPGA designs earlier in the development of the product, in order to debug and test designs. Architectures designed in HDL are easy to programme and verify. In addition, HDL is normally more readable compared to schematics, especially for huge scale circuits. [30]

Developers can programme their FPGA modules at 4 levels of design: (1) Algorithmic level, such as if, case and loop statement; (2) RTL (Register-Transfer level) level, to connect registers with Boolean equations; (3) Gate level, to have combinational logic with logic gates like OR and XOR; (4) Switch level, to design the transistor inside switches.

Verilog is also able to define the architecture to control the inputs and outputs of a simulation.

#### 2.1.3 Xilinx IP Cores

Conventional FPGA design would involve the user to manually write all the design code. It may not be the most practical way for producing the best performance for FPGA design. When writing the code for FIR or FFT algorithm manually in HDL, it can cost a lot of time, and it is also harder to verify them. Thus, Xilinx and other FPGA manufacturer provided IP (Intellectual Property) cores to simplify the design procedure.

IP cores are presented with a GUI (Graphic User Interface) and offer a parameterized tool which lets the developer choose and customize certain designs. This gives the developer a greater flexibility and reusability. Furthermore, this tool also have other advantages such as reducing the design risk, less errors, faster and better compiling, more efficient resources usage and better results of the design. Xilinx IP Cores cover a wide field of

designs in the field of DSP, like FIR filters, FFT and shift registers, which play important roles in designs described in this thesis.

| View Documents   | -                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP Symbol        | <sup><i>B</i> ×</sup> <i>logi</i> <sup><i>C</i></sup> <i>RE</i> <b>RAM-based Shift Register</b> <sub>xilinx.com:ip:c_shift_ram:11.</sub>                                                                  |

|                  | Component Name delay                                                                                                                                                                                      |

|                  | Register Type                                                                                                                                                                                             |

|                  | Please select the type of shift register to be generated:                                                                                                                                                 |

|                  | Fixed Length                                                                                                                                                                                              |

|                  | C Variable Length Lossless                                                                                                                                                                                |

|                  | Optimization                                                                                                                                                                                              |

|                  |                                                                                                                                                                                                           |

| d[15:0] → → q[15 | og C Speed                                                                                                                                                                                                |

| a(3:0)           | When a variable-length lossless RAM-based Shift Register is selected, this parameter specifies if the core is to be optimized for area or speed.                                                          |

| clk —            | Clocking Options                                                                                                                                                                                          |

| pe               | 🔽 Register Last Bit                                                                                                                                                                                       |

| soir             | Clock Enable (CE)                                                                                                                                                                                         |

| sinit>           | Dimensions                                                                                                                                                                                                |

| ssel             | Width 16 Range: 1256                                                                                                                                                                                      |

|                  | Depth 16 Range: 11088                                                                                                                                                                                     |

|                  | Latency Information                                                                                                                                                                                       |

|                  | Latency 0                                                                                                                                                                                                 |

|                  | Latency represents delay in addition to the Depth of the RAM-based shift register (SR). Additional latency is incurred with variable length SRs when Register Last Bit or Speed optimization is selected. |

|                  |                                                                                                                                                                                                           |

|                  |                                                                                                                                                                                                           |

|                  | Datasheet          Back         Page 1 of 3         Next >         Generate         Cancel         Help                                                                                                   |

Figure 2.3 Xilinx IP core GUI (Xilinx ISE 14.3)

Figure 2.3 illustrates the example of GUI form a Xilinx IP core. The parameterize factors can determine the control pins, data formation, optimization methods and some other configurations.

#### 2.1.4 Fixed point DSP

Digital signal processing can be separated into two categories – fixed point and floating point [31]. These refer to the format used to store the data in the devices. For a common 16 bits fixed point application, there are up to 65,536 possible bit patterns ( $2^{16}$ ). Signed fixed point value can use two's compliment to make the value include negative numbers [32]. For a common 32 bits floating point application, there are more bit patterns than

fixed point, which is  $2^{32}$  to be exact. A key feature of floating point presentation is that the numbers are not uniformly spaced [33].

Normally fixed point arithmetic is much faster than floating point in general purpose computers. The internal architecture of the floating point hardware is more complex than the fixed point hardware [31] as all the register and data should be 32 bits word length instead of 16, and all the multipliers and ALU must be able to process floating point arithmetic very fast. As a result, floating point has a better precision and higher dynamic range than fixed point but of greater size and thus cost. Fixed point dividers are usually cheaper than floating point devices.

In terms of performance, the biggest difference between the fixed point processing result and floating point processing result is SNR (Signal-to-Noise Ratio). When storing a 16bit fixed point value, the original number must be round up or down to its adjacent neighbour by a maximum of half of the gap size. Every time we round a number to fixed point presentation, noise will be added to the signal. Fixed point's rounding noise is much worse than floating point, because the gap between adjacent numbers is much larger than floating point. Usually fixed point has about 3000 times more quantization noise than floating point [31]. Thus these quantization error is a very important criteria in verifying the fixed point in future design.

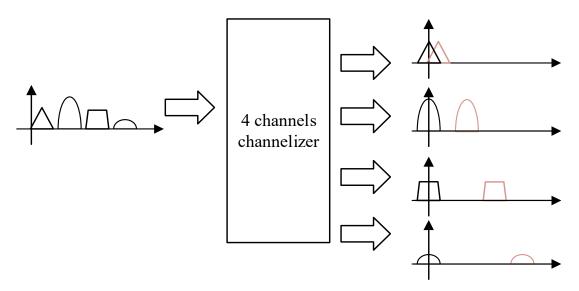

### 2.2 Channelization technology

Channelization is part of a digital signal processing that divides the wideband into separate channels, and down converts them to baseband, extracting one or more desired channels. The channels may have uniform or non-uniform allocation. Normally channelization is implemented by a down-converter and a low-pass filer [34]. Figure 2.4 illustrates a 4 channels channelizer. This wideband input signal has 4 interested channels, each of them is being filtered and down-converted to DC (baseband frequency), and is ready for following processing.

Figure 2.4 A 4 channels channelizer

#### 2.2.1 Single channel and multi-channel

Channelization technology is widely applied in the industry. For a mobile base (mobile phones), normally only one channel of signal is required to process. Thus the one-channel channelizer, which contains one down-converter and low-pass (or band-pass) filter can do a good job in this scenario.

#### 2.2.1.1 Per-channel approach

A base station needs to extract a large number of channels [35]. There are several ways to implement this job. The 'per-channel approach' is one of the most straightforward solutions for the multi-channel cases [34, 36, 37]. This approach operates K independent one-channel channelizers in parallel, where K is the number of channels. Each subchannel extracts one channel of interest in the wideband input, as shown in Figure 2.5. The 'per-channel approach' provides a high level of flexibility in the choice of channels' centre frequencies and bandwidths. Channels do not have the constraints of equal bandwidth or that of a uniform allocation. However, this kind of design would need many more hardware resources and power than other efficient designs, like polyphase filter-bank. As the down-converter requires quite a lot of complex multiplications and other operations, and as every channel requires its own down-converter, then as the number of channel K increases, the system complexity greatly increases. In higher sample rate applications, the 'per-channel approach' is not a wise option to implement channelization, as the current digital signal processer and FPGA cannot provide enough performance for this computational load.

Figure 2.5 Channelizer using per-channel approach to filter channels.

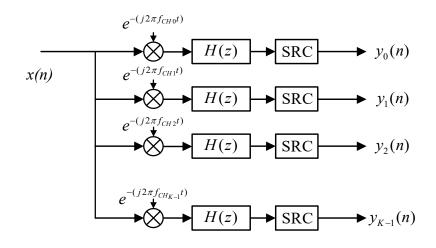

#### 2.2.1.2 Pipelined frequency transform

Another channelization technology is called pipelined frequency transform [38]. This technology occupies a structure, which contains a binary tree of DDCs (Digital Down Converters) followed by a number of SRCs (Sample Rate Converters). Every level of the tree divides the incoming wideband signal into a low frequency half and a high frequency half, and the next level divides these half bands again, until the tree's last level separates out the channels of interest [38]. This structure is also called QMF (Quadrature Mirror Filter) tree [39]. As a result, the system complexity is greatly reduced compared to the per-channel approach, because of the utilisation of the half band symmetry and sample rate reduction at each level.

The pipeline frequency transform offers a more efficient option in terms of hardware usage and power consumption compared to per-channel approach. This is especially in applications where a large number of channels are needed to be separated from the wide-band signal. However, it has weaknesses in terms of flexibility, as all the channels are required to have equal bandwidths and to be uniformly allocated. The diagram of pipeline frequency transform structure is shown in Figure 2.6

Background

Figure 2.6 Pipeline frequency transform structure of a binary tree with DDC followed by SRC.

#### 2.2.1.3 Polyphase filter-bank

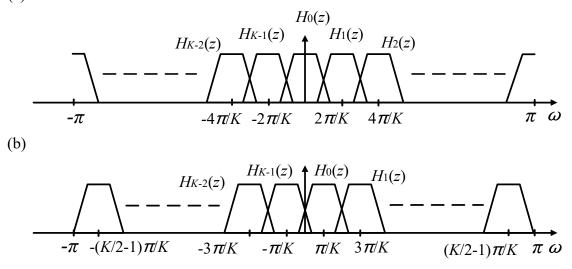

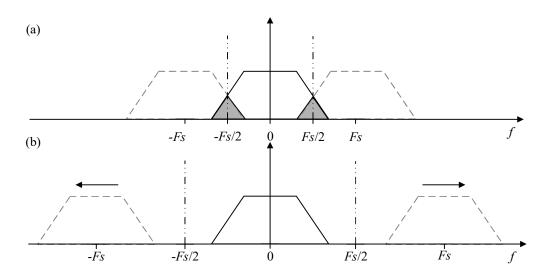

Computational efficient channelizers have been designed by using fast Fourier Transform (FFT) [40-42]. The polyphase filter offers further improvement in terms of efficiency. The operational efficiency and design simplicity is obtained from the fact that only one low-pass filter-bank is needed to be designed, and that the remaining band-pass filters will get their properties automatically after the modulation of the prototype filter. An analysis filter-bank will divide the wide-band signal uniformly (in the even stacked allocation), such that every sub-band would have the same space from its adjacent channels in the receiver side. (Even stacked means that there is one sub-band centred at DC, as shown in Figure 3.3 (a).

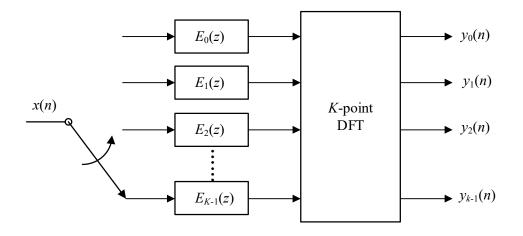

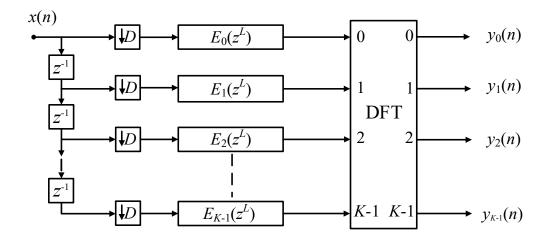

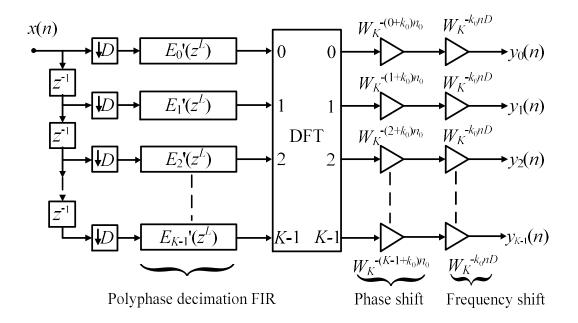

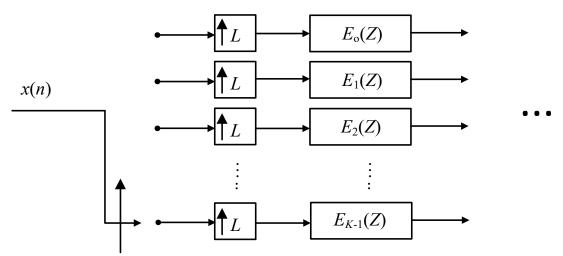

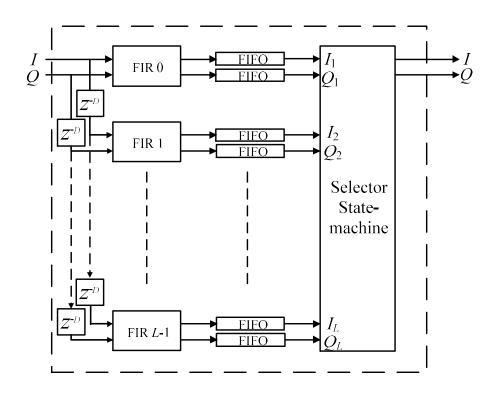

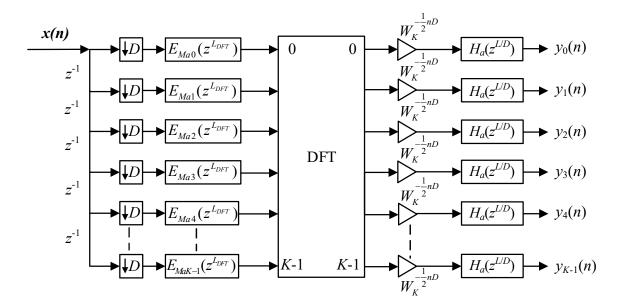

The structure of a polyphase filter-bank is shown in Figure 2.7. The input wideband signal samples will first be down-sampled and sent to polyphase decomposed filters. The filtered samples are then extracted using DFT. This type of channelizer are also referred to as DFT-FB (Discrete Fourier Transform Filter-Bank). DFT-FBs require that extracted channels in the wideband signal have to be uniformly allocated, and the signal sample rate has to be an integer multiple of the sub-channel's bandwidth. This is further discussed in chapter 3 as it is the base of the new implementations in the thesis.

Figure 2.7 The structure of the DFT-FB where *L* is the oversampling factor and  $E_K(z^L)$  are the polyphase components of the prototype filter H(z).

#### 2.2.2 Hardware complexity comparison

Hardware complexity comparisons between these three methods of channelization can be obtained from [17]. The detailed data is shown in Figure 2.1.

The comparisons are focused on the utilizations of LUTs and memory size. The utilization of LUTs is illustrated in Figure 2.8, and the memory size counted in bits comparison is illustrated in Figure 2.9.

| Channelization method        | Number of channels | LUTs      | Memory (bits) |

|------------------------------|--------------------|-----------|---------------|

|                              | 256                | 317,498   | 436,224       |

| Per-channel approach         | 512                | 650,114   | 876,544       |

|                              | 1024               | 1,336,754 | 1,761,280     |

|                              | 256                | 27,930    | 3,840         |

| Pipeline frequency transform | 512                | 32,270    | 6,529         |

|                              | 1024               | 36,610    | 10,625        |

|                              | 256                | 4,608     | 4,608         |

| DFT-FB                       | 512                | 4,793     | 4,793         |

|                              | 1024               | 5,345     | 5,345         |

Table 2.1 The hardware comparison of per-channel approach, pipeline frequency transform DFT-FB

### LUT utilization comparison

Figure 2.8 The LUT utilization comparison

In the comparison of the LUTs requirements, the Figure 2.8 shows that per-channel approach is a very inefficient channelization approach, it uses more LUT resources, which makes it difficult to compare between DFT-FB and pipelined frequency transform in the upper figure, and the situation will be much worse when the number of channels increases. From the lower plot of Figure 2.8, the clear LUT utilization comparison between DFT-FB and pipelined frequency transform shows that DFT-FB only requires about one third of the LUT resources that pipelined frequency transform uses.

### memory bits comparison

Figure 2.9 the memory bit comparison

In the memory usage comparison, a similar result to LUT resource usage is provided by the data as well. The inefficient per-channel approach still use much more memory resources than other two approaches. The memory comparison between DFT-FB and pipelined frequency transform in the lower plot of Figure 2.9 shows us that if the number of channels is smaller than 256, the pipeline frequency transform will use slightly less memory than DFT-FB; however, for applications of more than 256 channels, the DFT-FB will have a lower memory usage than pipelined frequency transform, and further efficiency will be obtained as the channel number increases. Based on the analysis of LUTs on memory usage and that the number of channels in industrial application is normally greater than 256, DFT-FB is the preferred approach for further development.

#### 2.2.3 Uniform Versus Non-uniform

In digital signal processing, the down-sample rate and the filter-response in a filter-bank are the same across all the channels in the wideband signal, in this case the system is considered as a uniform filter-bank. An illustration of the frequency response of uniform filter-bank is shown in Figure 2.10.

Figure 2.10 The uniform filter-bank's frequency response

There are some further developments based on DFT-FB in the literature that provide nonuniformly bandwidth channel allocation configurations. [7, 43] developed a non-uniform P-GDFT (Parallel GDFT) to achieve DFSA (Dynamic Fragment Sub-band Allocation).

The structure of P-GDFT is shown in Figure 2.11. This type of non-uniform channelizer employs multiple different bandwidth polyphase filter-banks in parallel, to process the same wideband input signal simultaneously. Every filter-bank implements a uniform channel extraction of the wideband by its own filtering specification. The channels of interest are extracted by selecting the needed outputs from each polyphase filter-bank. P-GDFT has a high ratio of non-used channels, and the process of the non-used channels cannot be avoided, because all the channels contribute to the overall computational load. This means that there is a lot of waste in terms of resources usage in the hardware implementation.

Figure 2.11 P-GDFT non-uniform structure

[7, 43] also carried out another non-uniform channelizer called R-GDFT (Recombined GDFT), as shown in Figure 2.12. The basic idea of R-GDFT is to let a polyphase filterbank channelize the wideband signal first, and then extract the channel of interest by recombining two or more adjacent channels according to specific requirements of different standards. The bandwidth of the polyphase filter-bank is also known as *granularity band*. The smaller the granularity band is, the more options in bandwidth and centre frequencies of sub-bands.

Figure 2.12 Recombined GDFT-FB channelizer

Although R-GDFT can have a better computational efficiency, its re-configurability level is lower than the P-GDFT's, because in the R-GDFT each type of channel can only be centred at the multiple of its channel spacing. In addition, to meet a new standard requirement, P-GDFT only needs partly tuning or adding one more polyphase filter-bank with the new specification.

### 2.3 Frequency Response Masking (FRM)

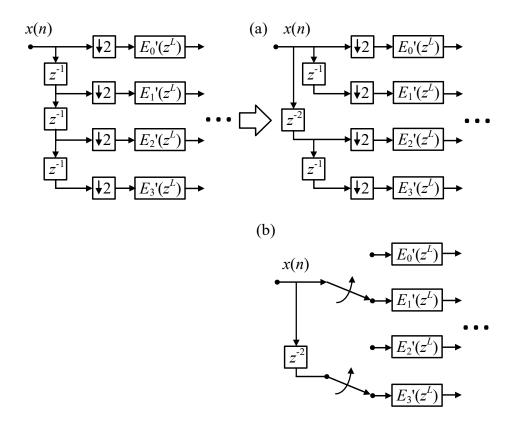

The first concept of Frequency Response Masking (FRM) technology was developed in [44], in order to reduce the complexity of designing a linear phase FIR filter with a very sharp transition band. The reduction of FIR design complexity is achieved by employing the cascading connection of an interpolated FIR filter and a FIR filter with a relaxed specification, instead of designing one FIR filter with a very restricted specification. The interpolated FIR filter is obtained by replacing the unit delay  $Z^{-1}$  with the delay  $Z^{-L}$ , where L is an integer number. In other words, put L-1 zeros in every adjacent coefficients of the FIR filter. After this, the FIR filter's frequency response will become periodic. Then the other following relaxed designed FIR filter will mask the duplicate images produced by the interpolated FIR filter.

A much more practical approach has been developed in [45], for applying FRM when designing a sharp linear phase digital filter in a narrow-band or an arbitrary-band. The structure is designed in a parallel form with two branches of cascaded FRM structures mentioned in last paragraph, as shown in the Figure 2.13.

Figure 2.13 Direct form of frequency response masking

In the diagram, the branch on the top is normally called the *positive* branch and the other one on the bottom is normally called the *complementary* branch. All the four linear phase FIR filters have much more relaxed filtering specification compared to the initial single directly designed FIR filter. As a result, fewer non-zero coefficients and multiply operations are required by the FRM structure to have a sharp filter response. The computational load would have a significant reduction along with the computational load of the directly designed FIR filter having the equivalent filtering specification. The process of how to filter in both top and bottom FRM branches, and how to sum them together to result the final desired filtering frequency response is shown in Figure 2.14.

Figure 2.14 The process of two branches filtering base on FRM

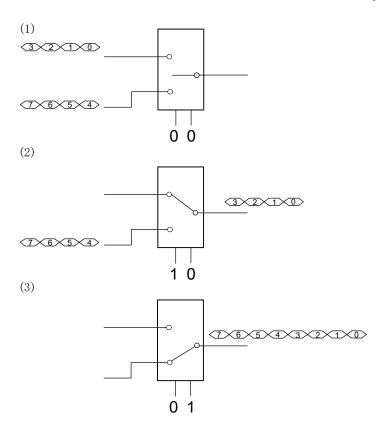

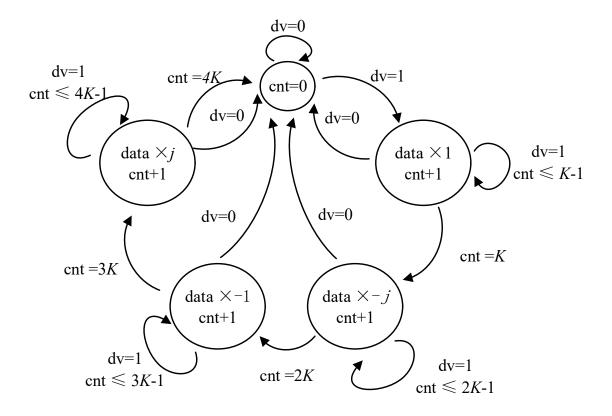

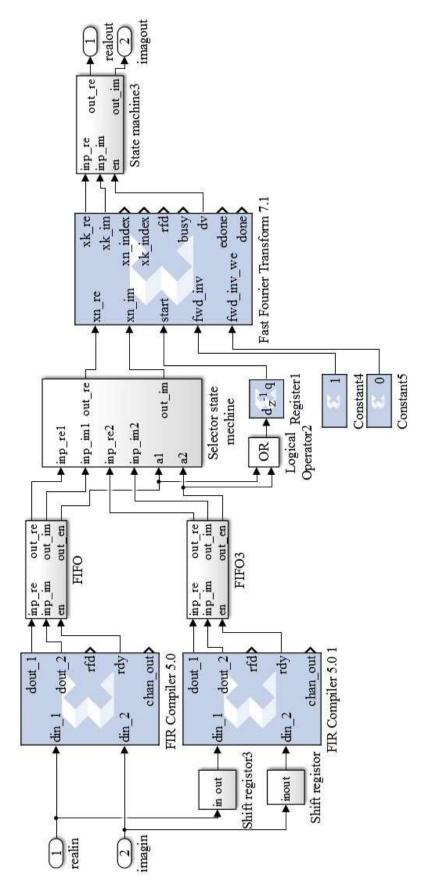

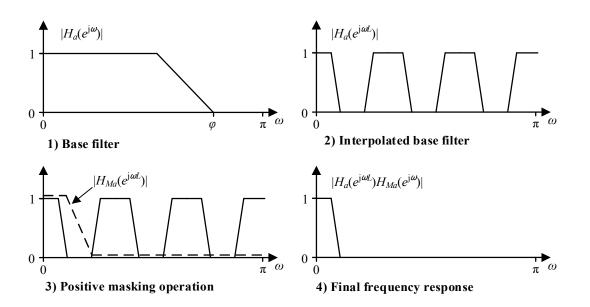

In the FRM structure, the base filter is  $H_a(z)$  and the complementary filter is  $H_c(z)$ . Their frequency responses are shown in Figure 2.14 (1) [46]. Both of them are then interpolated by a factor L by adding L-1 zeros in every adjacent coefficient of the FIR filter. Thus the passbands of  $H_a(z)$  and  $H_c(z)$  are reduced L times, and the transition band is L times sharper. All the filtering frequency responses are centred at  $2\pi/L$ . After that, the masking filters  $H_{Ma}(z)$  and  $H_{Mc}(z)$  will filter the interpolated frequency responses of base and complementary filter, thus only useful replicas will be left. In the end, by adding useful base and complementary replicas, the desired sharper filtering response will be finally produced.

Figure 2.15 Efficient implementation of FRM

The transfer function of the FRM parallel structure is:

$$H(z) = H_a(z^L)H_{Ma}(z) + H_c(z^L)H_{Mc}(z)$$

(2.1)

where  $H_a(z)$  is the base filter, and  $H_c(z)$  is its complementary filter, and  $H_{Ma}(z)$ ,  $H_{Mc}(z)$ are the masking filters for interpolated bass filter and complementary filter respectively. If  $N_a$  is the order of the base filter, the complementary filter  $H_c(z)$  has a relationship with base filter  $H_a(z)$  given as:

$$H_c(z) = z^{-(N_a/2)} - H_a(z)$$

(2.2)

Hence, the relationship between interpolated base filter and complementary filter can be expressed as:

$$H_c(z^L) = z^{-L(N_a/2)} - H_a(z^L)$$

(2.3)

Therefore the complementary filter can be implemented by a chain of delays subtracting the base filter output. This will guide us to an efficient FRM structure as shown in Figure 2.15.

#### 2.3.1 Subclass I filter

It has been discussed in the previous section that the transform function of whole FRM filter is given by equation (2.1). From the description of [45], the specifications of passband  $\omega_p$  and stopband  $\omega_s$  of the base filter  $H_a(z)$  can be both freely selected. In addition, the complementary filter  $H_c(z)$  can be also determined by equation (2.2) in order to implementing a further efficient FRM module illustrated in Figure 2.15.

However, a new class of FRM FIR filters called subclass I filter can be obtained only if we can ensure that the relationship between base filter  $H_a(z)$  and complementary filter  $H_c(z)$  can be expressed as:

$$H_c(z) = H_a(-z) \tag{2.4}$$

In order to match this condition, this special class of FRM filter must be designed with a base band filter whose transition band includes the normalized frequency  $\pi/2$  [47], as shown in Figure 2.16.

Figure 2.16 Subclass I Filter frequency response

In this circumstance, the computational load of the whole FRM structure could be further reduced if both branches share the same polyphase component as:

Background

$$H_a(z) = H_{a0}(z^2) + z^{-1}H_{a1}(z^2)$$

(2.5)

where  $H_{a0}(z)$  and  $H_{a1}(z)$  are the polyphase components of  $H_a(z)$ . Then the base filter  $H_c(z)$  can be expressed as:

$$H_{c}(z) = H_{c0}(z^{2}) + z^{-1}H_{c1}(z^{2}) = H_{a0}(z^{2}) - z^{-1}H_{a1}(z^{2})$$

(2.6)

Thus when (2.6) is applied into (2.1), the whole new efficient design of FRM structure called full FRM is obtained as illustrated in Figure 2.17. This method makes the whole FRM filter design simpler than the design shown in Figure 2.15, as only  $H_a(z)$ ,  $H_{Ma}(z)$  and  $H_{Mc}(z)$  need to be designed, and the usage of polyphase components of  $H_a(z)$  takes the places of two complete filters.

Figure 2.17 The efficient FRM design with polyphase decomposition

### 2.4 TETRA standard

TETRA (Terrestrial Trunked Radio) is a set of wireless digital telecommunication standards developed by the European Telecommunications Standardisation Institute (ETSI) that describes a common mobile radio communications infrastructure throughout Europe. TETRA provides reliable and robust digital communications to Professional Mobile Radio (PMR) and Public Access Moible Radio (PAMR) applications [48, 49]. These applications are targeted primarily at the mobile radio needs of public safety groups (such as police and fire departments), utility companies, and other enterprises that provide voice and data communications services.

In contrast with existing commercial mobile communication standards, PMR communication systems offer improved communication capabilities such as strong encryption information security, direct-mode to allow end-2-end communication without a base station, very long distance transmission [50]. Furthermore, comparing to commercial communication standards, PMR standards are basically allocated lower frequency bands, thus the wireless channel will produce less free-space attenuation over the transmitted signals.

TETRA is a fully digital system providing consistent voice quality and low bit error rate for data accordingly. It supports voice, circuit switched data and packet switched data services with a wide selection of data transmission rates and error protection levels.

For its modulation, TETRA uses  $\pi/4$  Differential Quadrature Phase-Shift Keying (DQPSK). The symbol (baud) rate is 18,000 symbols per second, and each symbol maps to 2 bits, thus resulting in 36 kbit/s gross.

TETRA also uses Time Division Multiple Access (TDMA) technology. The process of TDMA involves digitally modulating a single frequency in order to increase the number of independent communication channels. Specifically it uses 4 channels interleaved into one 25 kHz channel. Instead of just one user being able to use the single 25 kHz channel, it can now be used by up to 4 different users. This creates both a cost savings in frequency needed and base stations or repeaters needed. It can support a gross bit rate of 36 kbits/s, with 7.2k bits/s per TDMA channel. The difference in the 28.8 kbits/s (4\*7.2) is from overhead of the TDMA structure.

Each TDMA frame of four slots is grouped further as 18 frames, which, combined, form a multiframe. In circuit mode (as opposed to packet mode) voice and data, is compressed into 17 TDMA frames allowing for a control signaling frame to be used without stopping the flow of data.

# 2.5 Related work

In this section, we review the relevant works of the polyphase filter-banks.